Spec. No. : C151N6 Issued Date : 2012.11.08 Revised Date : Page No. : 1/11

# Current Mode PWM Controller MC7773N6

## Description

MC7773N6 is a highly integrated current mode PWM control IC optimized for high performance low standby power offline flyback converter applications.

To meet the international power conservation requirements, optimized green mode is integrated to improve the efficiency at light or no load conditions with no audible noise.

Slope compensation is integrated to ensure the stability at high load. Lead edge blanking is integrated to prevent the false trigger at the transition of the switch. Soft switching control at the gate drive can improve the EMI performance of the power supply. The Gate-drive output is clamped at 12V to protect the power MOS.

## **Features**

- •Frequency jitter function to improve EMI performance of power supply

- •No-audible-noise green mode control

- •Multi operation mode: Fixed-frequency CCM, green mode and burst mode.

- •No load input power under 100mW

- •Internal slope compensation

- •Low VDD startup current and low operating current

- •Leading edge blanking

- •UVLO 8.5V / 15.5V

- •Gate max output voltage clamp at 12V

- Overload Protection (OLP) with auto-recovery

- •Line compensation over current protection (OCP) with auto-recovery

- •Over Temperature Protection (OTP) witch latch

- VDD Over Voltage Protection (OVP) witch latch

## **Applications**

Offline AC/DC flyback converter for

- Battery Charger

- Power Adaptor

- Set-Top Box Power Supplies

- Open-frame SMPS

- PC 5V Standby Power

## **Ordering Information**

| Device   | Package                             | Shipping               |

|----------|-------------------------------------|------------------------|

| MC7773N6 | SOT-23-6L<br>(Pb-free lead plating) | 3000 pcs / tape & reel |

Spec. No. : C151N6 Issued Date : 2012.11.08 Revised Date : Page No. : 2/11

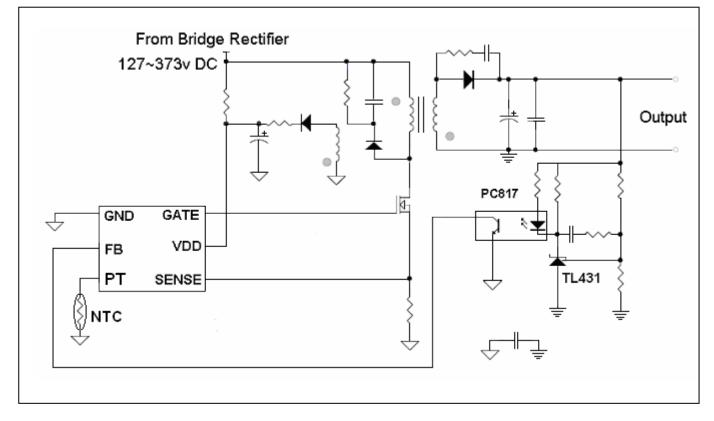

# **Typical Application Circuit**

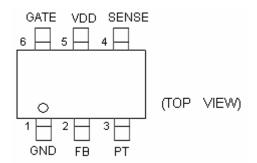

# **Pin Configuration**

# **Pin Assignment**

| Pin Name | Pin Number | Pin Function                                                                                                                                                     |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND      | 1          | Ground                                                                                                                                                           |

| FB       | 2          | Feedback input pin. The PWM duty cycle is determined by voltage level into this pin and the current-sense signal at Pin 6.                                       |

| РТ       | 3          | Connected through a NTC resistor to ground for over temperature shutdown/latch control or connected through Zener to VDD for adjustable over voltage protection. |

| SENSE    | 4          | Current sense input pin. Connected to MOSFET current sensing resistor node.                                                                                      |

| VDD      | 5          | Chip DC power supply pin.                                                                                                                                        |

| GATE     | 6          | Totem-pole gate drive output for the power MOSFET.                                                                                                               |

Spec. No. : C151N6 Issued Date : 2012.11.08 Revised Date : Page No. : 3/11

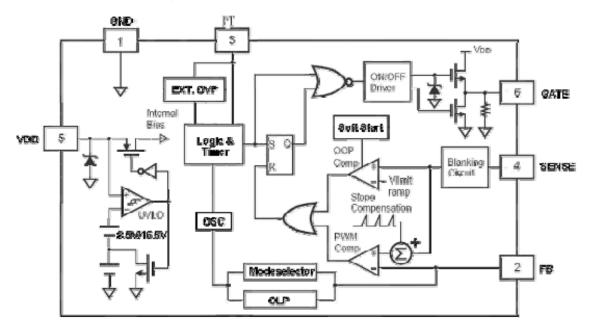

## **Function Block Diagram**

#### **Absolute Maximum Ratings**

| Parameter                             | Value      | Unit |

|---------------------------------------|------------|------|

| VDD to GND                            | +29        | V    |

| VDD clamped current                   | 10         | mA   |

| VDD clamped voltage                   | 32         | V    |

| VFB, VSENSE and VRI to GND            | -0.3~+7    | V    |

| Maximum Junction Temperature (Tj MAX) | -20 ~ +150 | °C   |

| Storage Temperature Range             | -55 ~ +160 | °C   |

Note: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

## **Recommended Operating Conditions**

| • Supply Voltage, VDD                                                  | +10V to +30V                             |

|------------------------------------------------------------------------|------------------------------------------|

| Operating Temperature Range                                            | $\dots -20^{\circ} C$ to $+85^{\circ} C$ |

| • Power Dissipation (R <sub>0JA</sub> =250 °C/W) @25 °C, FR-4 PCB, 2oz | 0.4W                                     |

## **ESD** Information

| Human Body Mode | 2000V |

|-----------------|-------|

| Machine Mode    | 200V  |

## **Electrical Characteristics**

$(T_A = 25^{\circ}C, V_{DD} = 16V \text{ if not otherwise noted})$

| Parameter                                                | Symbol   | Test Conditions                         | Min  | Тур   | Max  | Units |

|----------------------------------------------------------|----------|-----------------------------------------|------|-------|------|-------|

| SUPPLY SECTION                                           |          |                                         |      |       |      |       |

| Chip start up current via VDD pin                        | I_set    | Vdd=12V, measure current into VDD pin   |      | 3     | 20   | uA    |

| Operation current                                        | l_op     | _op VDD=16V,VFB=3V                      |      |       |      | mA    |

| VDD UVLO enter                                           | UVLO_L   |                                         | 7.5  | 8.5   | 9.5  | V     |

| VDD UVLO exit                                            | UVLO_H   |                                         | 14.5 | 15.5  | 16.5 | V     |

| VDD OVP                                                  | VDD_OVP  |                                         | 30   | 32    | 34   | V     |

| VZ(VDD clamp voltage)                                    | VDD_CLP  | lz(ldd)=10mA                            | 30   | 32    | 34   | V     |

| FEEDBACK SECTION                                         |          |                                         |      |       |      |       |

| PWM input gain                                           | A_PWM    | ΔVFB/ΔVCS                               |      | 2     |      | V/V   |

| VFB open loop voltage                                    | VFB_O    |                                         |      | 4.2   |      | V     |

| FB pin short circuit current                             | VFB_S    | Short FB pin to gnd and measure current |      | 0.35  |      | mA    |

| Burst mode on threshold                                  | V_BM_on  |                                         |      | 0.675 |      | V     |

| Burst mode off threshold                                 | V_BM_off |                                         |      | 0.575 |      | V     |

| Power limiting FB threshold                              | VFB_th_P |                                         |      | 3.7   |      | V     |

| Power limiting delay time                                | T_PL_D   |                                         |      | 88    |      | ms    |

| Input impedance                                          | R_FB     |                                         |      | 16    |      | KΩ    |

| OSCILLATOR                                               | 1        |                                         |      |       |      |       |

| Soft start time                                          | T_ss     |                                         |      | 4     |      | ms    |

| Burst mode switching frequency                           | F_burst  |                                         |      | 22    |      | kHz   |

| Normal operation frequency                               | F_nor    |                                         | 60   | 65    | 70   | kHz   |

| Frequency modulation range                               | F_d_jit  |                                         |      | ±4    |      | %     |

| Jitter frequency                                         | F_jitter |                                         |      | 32    |      | Hz    |

| Frequency temperature stability                          | F_d_tem  |                                         |      | 4     |      | kHz   |

| CURRENT SENSE SECTION                                    |          |                                         |      |       |      |       |

| Leading edge blanking time                               | T_blank  |                                         |      | 220   |      | nS    |

| Sense pin input impedance                                | R_sense  |                                         |      | 40    |      | kΩ    |

| Over current threshold voltage at zero duty cycle        | VTH_OC_0 | FB=3.3V                                 | 0.72 | 0.75  | 0.78 | v     |

| Over current threshold voltage at max. switching on time | VTH_OC_1 | FB=3.3V                                 |      | 0.9   |      | V     |

| Over current protect delay                               | T_OC_D   | CS>VTH_OC, FB=3.3V, CL=1nF<br>@Gate     |      | 120   |      | nS    |

| GATE OUTPUT                                              | 1        | 1                                       | I    | 1     |      | 1     |

| Output low level                                         | VOL      | lo=20mA                                 |      |       | 1    | V     |

| Output high level                                        | VOH      | lo=20mA                                 | 6    |       |      | V     |

| Output voltage clamped level                             | VO_clamp |                                         |      | 12    |      | V     |

| Output rising time                                       | Tr       | Cl=1nf                                  |      | 175   |      | nS    |

| Output falling time                                      | Tf       | Cl=1nf                                  |      | 85    |      | ns    |

| PT Pin                                                   | 1        | 1                                       |      | I     |      | 1     |

| PT pin source current                                    | I_PT     |                                         | 95   | 100   | 105  | μA    |

| Thresh hold of OTP                                       | V_OTP    |                                         | 0.95 | 1     | 1.05 | V     |

Spec. No. : C151N6 Issued Date : 2012.11.08 Revised Date : Page No. : 5/11

| OTP debounce time          | T_OTP   |  | 6   | cycle |

|----------------------------|---------|--|-----|-------|

| External OVP trigger point | Vth_OVP |  | 4   | V     |

| Float voltage at PT pin    | V_PT_FL |  | 2.3 | V     |

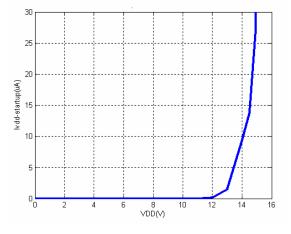

## Typical Characteristics (TA = 25°C, VDD=16V if not otherwise noted.)

Start Current Vs VDD Voltage

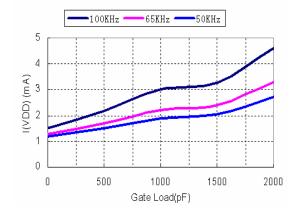

**Operation Current VS Load**

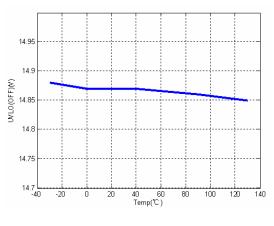

UVLO (Off) Voltage VS Temp

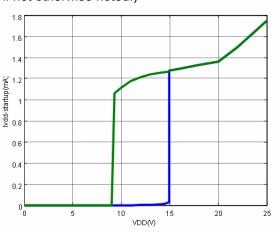

UVLO Voltage& Operation Current

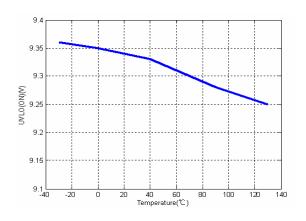

UVLO (On) Voltage VS Temp

Spec. No. : C151N6 Issued Date : 2012.11.08 Revised Date : Page No. : 6/11

## **OPERATION DESCRIPTION**

#### **Over-view description**

The MC7773N6 includes all necessary function to build an easy and cost effective solution for low power supplies to meet the international power conservation requirements.

#### Start-up current

Startup current of MC7773N6 is designed to be very low so that VDD could be charged up above UVLO (exit) threshold level and device starts up quickly. Also a large value startup resistor can be used to minimize the power loss.

#### Green Mode Operation (Patent)

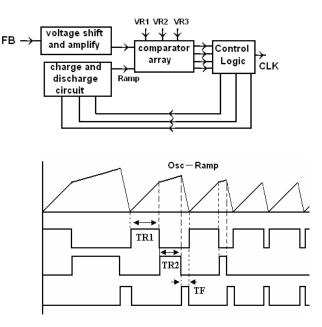

At light load or no load condition, the switch loss become the major loss of the power supply, to reduce the power wasted in light and no load condition, based on a special designed voltage controlled oscillator, green mode operation of the power supply can be achieved by using MC7731N6. The controller will judge the load condition based on the voltage of FB pin. In light load the FB voltage will decrease, when VFB is lower than a set threshold voltage, a FB depending time (TR2) will be generated by the oscillator and decrease the operating frequency of the power supply, the minimum frequency is set about 22kHZ. The function block and the working waveform can be depicted as below:

When V<sub>FB</sub> decreases further, the power supply will enter into burst mode operation to decrease the power consumed at no load condition. Besides there is no audible noise in any load condition.

Spec. No. : C151N6 Issued Date : 2012.11.08 Revised Date : Page No. : 7/11

#### **Built-in Slope Compensation and Frequency Shuffling**

While MC7773N6 works in CCM mode, slope compensation and frequency shuffling is activated. The sensed voltage across the sense resistor is used for pwm control, and pulse by pulse current limit, Built-in slope compensation circuit adds a voltage ramp onto the current sense input voltage. This greatly improves the close loop stability and prevents the sub-harmonic oscillation of peak current mode pwm control scheme.

To improve the EMI performance, the frequency of CCM mode is shuffling to 65kHz  $\pm 4$ %.

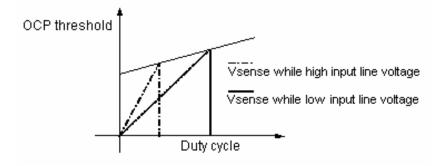

#### Line Slope Compensation

Adjusting the RSENSE can set the Max output power of the power supple mode. The current flowing by the power MOSFET has an extra value due to the system delay T that the current detected from the sense pin to power MOSFET cut off in the MC7773N6. To guarantee the output power is a constant for universal input AC voltage, there is a positive ramp signal to compensate the system delay T and the line input. At lower line-input voltage the higher OCP threshold will bring constant power OCP as below.

#### Leading Edge Blanking

Each time when the power MOSFET is switched on, a turn-on spike will inevitably occur on the sense-resistor. To avoid premature termination of the switching pulse, a 300 nsec leading-edge blanking time is built in. Conventional RC filtering can therefore be omitted. During this blanking period, the current-limit comparator is disabled and it cannot switch off the gate driver.

#### **Gate Driver**

The output stage of MC7773N6 is a fast totem pole gate driver. Cross conduction has been avoided to minimize heat dissipation, increases efficiency and enhances reliability. The output driver is clamped by an internal 18V Zener diode in order to protect power MOSFET transistors against undesirable gate over voltage. A soft driving waveform is implemented to minimize EMI.

Spec. No. : C151N6 Issued Date : 2012.11.08 Revised Date : Page No. : 8/11

#### **Protect Functions**

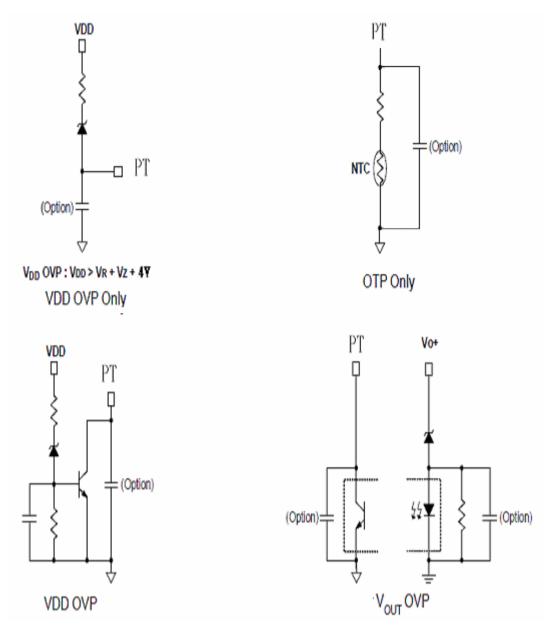

To increase the reliability of power supply system many protection functions is integrated in this controller, including Cycle-by-Cycle current limiting (OCP), Over Load Protection (OLP), Over Temperature Protection(OTP), External Over Voltage Protection (OVP) and over voltage clamp, Under Voltage Lockout on VDD (UVLO). At overload condition when FB input voltage exceeds power limit threshold value for more than TD\_PL (power limit debounce time), the controller reacts to shut down the output power MOSFET. Device restarts when VDD voltage drops below UVLO limit. VDD is supplied by transformer auxiliary winding output. It is clamped when VDD is higher than threshold value. The power MOSFET is shut down when VDD drops below UVLO limit and device enters power on start-up sequence thereafter. Pin floating protection for CS, FB, PT is also added. While one of this happens, the GATE is turned off.

#### **PT Pin Typical Application Circuit**

Spec. No. : C151N6 Issued Date : 2012.11.08 Revised Date : Page No. : 9/11

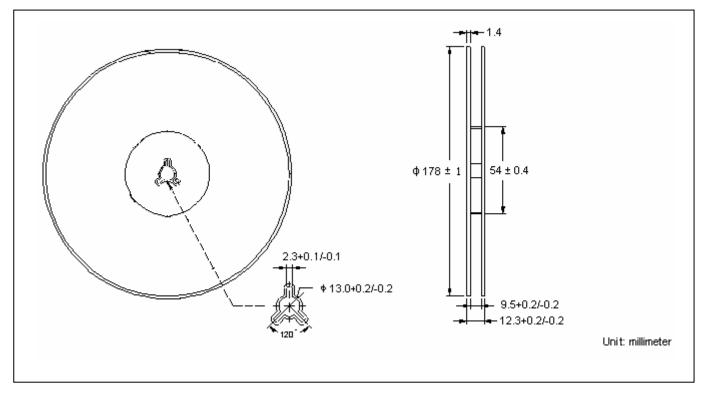

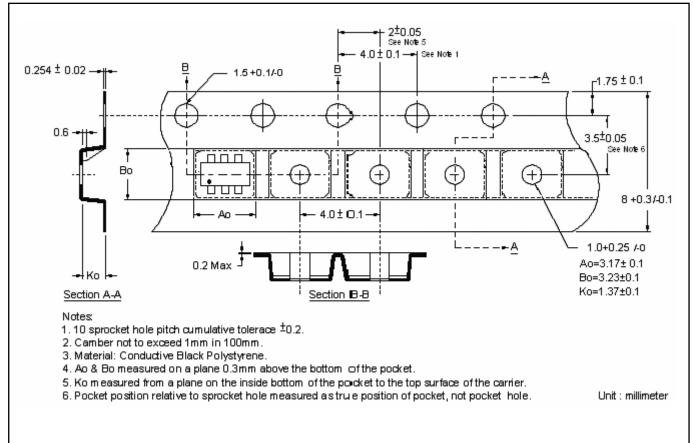

## **Reel Dimension**

## **Carrier Tape Dimension**

#### **Recommended wave soldering condition**

| Product         | Peak Temperature | Soldering Time  |

|-----------------|------------------|-----------------|

| Pb-free devices | 260 +0/-5 °C     | 5 +1/-1 seconds |

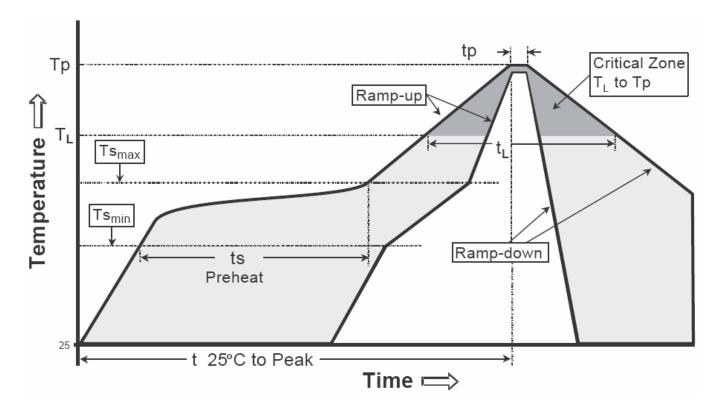

## Recommended temperature profile for IR reflow

| Profile feature                                | Sn-Pb eutectic Assembly | Pb-free Assembly |

|------------------------------------------------|-------------------------|------------------|

| Average ramp-up rate<br>(Tsmax to Tp)          | 3°C/second max.         | 3°C/second max.  |

| Preheat                                        |                         |                  |

| -Temperature Min(Ts min)                       | 100°C                   | 150°C            |

| -Temperature Max(Ts max)                       | 150°C                   | 200°C            |

| -Time(ts min to ts max)                        | 60-120 seconds          | 60-180 seconds   |

| Time maintained above:                         |                         |                  |

| –Temperature (TL)                              | 183°C                   | 217°C            |

| – Time (t∟)                                    | 60-150 seconds          | 60-150 seconds   |

| Peak Temperature(T <sub>P</sub> )              | 240 +0/-5 °C            | 260 +0/-5 °C     |

| Time within 5°C of actual peak temperature(tp) | 10-30 seconds           | 20-40 seconds    |

| Ramp down rate                                 | 6°C/second max.         | 6°C/second max.  |

| Time 25 °C to peak temperature                 | 6 minutes max.          | 8 minutes max.   |

Note : All temperatures refer to topside of the package, measured on the package body surface.

Spec. No. : C151N6 Issued Date : 2012.11.08 Revised Date : Page No. : 11/11

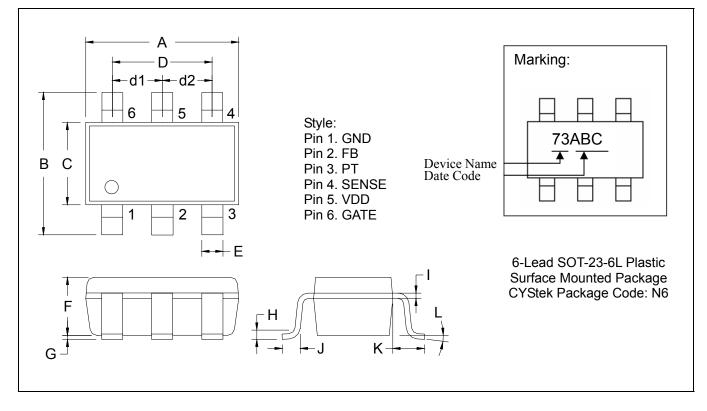

## SOT-23-6L Dimension

| DIM - | Inches |        | Millimeters |      | DIM | Inches     |        | Millimeters     |      |

|-------|--------|--------|-------------|------|-----|------------|--------|-----------------|------|

| DIN   | Min.   | Max.   | Min.        | Max. |     | Min.       | Max.   | Min.            | Max. |

| А     | 0.1063 | 0.1220 | 2.70        | 3.10 | F   | 0.0472 REF |        | 1.20 REF        |      |

| В     | 0.1024 | 0.1181 | 2.60        | 3.00 | G   | 0          | 0.0059 | 0               | 0.15 |

| С     | 0.0551 | 0.0709 | 1.40        | 1.80 | Н   | -          | 0.0086 | -               | 0.22 |

| D     | 0.074  | 8 REF  | 1.90        | REF  |     | 0.0047 REF |        | 0.12 REF        |      |

| d1    | 0.0374 | 4 REF  | 0.95        | REF  | J   | 0.0146 REF |        | 0.37 REF        |      |

| d2    | 0.0374 | 4 REF  | 0.95        | REF  | K   | 0.0236 REF |        | 0.0236 REF 0.60 |      |

| E     | 0.0118 | 0.0217 | 0.30        | 0.55 | L   | <b>0</b> ° | 10°    | 0°              | 10°  |

|       |        |        |             |      |     |            |        |                 |      |

Notes: 1.Controlling dimension: millimeters.

2.Maximum lead thickness includes lead finish thickness, and minimum lead thickness is the minimum thickness of base material.3.If there is any question with packing specification or packing method, please contact your local CYStek sales office.

Material :

• Mold Compound : Epoxy resin family, flammability solid burning class:UL94V-0.

#### Important Notice:

• All rights are reserved. Reproduction in whole or in part is prohibited without the prior written approval of CYStek.

• CYStek reserves the right to make changes to its products without notice.

• CYStek semiconductor products are not warranted to be suitable for use in Life-Support Applications, or systems.

• CYStek assumes no liability for any consequence of customer product design, infringement of patents, or application assistance.